Apic — io apic mode

Содержание:

Masking

The PIC has an internal register called the IMR, or the Interrupt Mask Register. It is 8 bits wide. This register is a bitmap of the request lines going into the PIC. When a bit is set, the PIC ignores the request and continues normal operation. Note that setting the mask on a higher request line will not affect a lower line. Masking IRQ2 will cause the Slave PIC to stop raising IRQs.

Here is an example of how to mask an IRQ:

void IRQ_set_mask(unsigned char IRQline) {

uint16_t port;

uint8_t value;

if(IRQline < 8) {

port = PIC1_DATA;

} else {

port = PIC2_DATA;

IRQline -= 8;

}

value = inb(port) | (1 << IRQline);

outb(port, value);

}

void IRQ_clear_mask(unsigned char IRQline) {

uint16_t port;

uint8_t value;

if(IRQline < 8) {

port = PIC1_DATA;

} else {

port = PIC2_DATA;

IRQline -= 8;

}

value = inb(port) & ~(1 << IRQline);

outb(port, value);

}

On-Demand Clock Modulation что это?

On-Demand Clock Modulation (ODCM) — устаревшая технология модуляции тактовой частоты процессора по запросу. Простыми словами — снижение частоты при перегреве, то есть что-то вроде троттлинга. Если процессор перегревается, то снижение частоты приведет к снижению температуры.

- Опция может быть расположена в разделе Advanced > CPU Configuration. Значения могут быть Auto, Enabled, Disabled, 12.5% On, 25.0% On, 37.5% On, 50.0% On, 62.5% On, 75.0% On и 87.5% On. По умолчанию должно стоять Auto.

- Опция была актуальна во времена Pentium 4. Тогда была проблема с процессорами, когда производительность падала, и решение оказывалось в отключении On-Demand Clock Modulation.

- Предположительно другое название функции — Clock Modulation.

- При разгоне вроде как нужно отключать (впрочем советую отключать и энергосберегательные технологии).

Я нашел информацию в одном журнале. Толком что имеется ввиду — не знаю. Похоже на принудительный пропуск тактов. Но опять же — я не могу точно понять. А не могу, потому что инфа была на английском, я перевел на русский.. и вот перевод:

Еще из-за включенной функции могут быть ошибки в старых играх. Например есть какая-то ошибка 200 в игре Jazz Rabbit 1994 и причина именно в On-Demand Clock Modulation. Странно, но вроде бы это относится и к игре Dota 2 — могут быть глюки при включенной функции.

Технологией On-Demand Clock Modulation можно как-то управлять. Умеют это делать например программы OverSoft CPU Informer, RightMark CPU Clock Utility.

Опция в биосе и программы OverSoft CPU Informer и RightMark CPU Clock Utility

вопросы

Существует ряд известных ошибок в реализации систем APIC, особенно в отношении того, как подключен 8254 . Дефектные BIOS могут неправильно настроить маршрутизацию прерываний или предоставлять неверные таблицы ACPI и таблицы Intel MultiProcessor Specification (MPS).

APIC также может быть причиной сбоя системы, если операционная система не поддерживает его должным образом. В старых операционных системах часто приходилось отключать I / O и локальные APIC. Хотя это больше невозможно из-за преобладания симметричных многопроцессорных и многоядерных систем, ошибки в прошивке и операционных системах сейчас редкость.

Интегрированные локальные APIC

Локальные APIC (LAPIC) управляют всеми внешними прерываниями для определенного процессора в системе SMP. Кроме того, они могут принимать и генерировать межпроцессорные прерывания (IPI) между LAPIC. LAPIC могут поддерживать до 224 используемых векторов прерываний от APIC ввода-вывода. Номера векторов от 0 до 31, от 0 до 255, зарезервированы для обработки исключений процессорами x86.

Все процессоры Intel, начиная с микроархитектуры P5 ( P54C ), имеют встроенный локальный APIC. Однако, если локальный APIC отключен в процессоре P5, он не может быть повторно включен программным обеспечением; это ограничение больше не существует в процессорах P6 и более поздних версиях.

Функция прерывания с сигнализацией сообщений (MSI) спецификации PCI 2.2 и более поздних версий не может использоваться без включения локального APIC. Использование MSI устраняет необходимость в APIC ввода-вывода. Кроме того, в режиме MSI поддерживается до 224 прерываний, а совместное использование IRQ не допускается.

Таймер APIC

Еще одно преимущество локального APIC заключается в том, что он также предоставляет таймер с высоким разрешением (порядка одной микросекунды или лучше), который можно использовать как в интервальном, так и в одноразовом режиме.

У таймера APIC были свои первые проблемы с приемкой. В документе Microsoft от 2002 года (который выступал за принятие вместо него высокоточного таймера событий ) критиковался таймер LAPIC за «плохое разрешение» и утверждается, что «микросхема часов иногда очень глючит». Тем не менее, таймер APIC используется, например, в Windows 7, когда профилирование включено, и в Windows 8 при любых обстоятельствах. (До того, как Windows 8 заявила об исключительных правах на этот таймер, он также использовался некоторыми программами, такими как CPU-Z .) В Microsoft Windows таймер APIC не является общим ресурсом.

Апериодические прерывания, предлагаемые таймером APIC, используются функцией ядра Linux без тиков

. Эта необязательная, но стандартная функция появилась в версии 2.6.18. Когда он включен на компьютере с таймером APIC, ядро не использует программируемый интервальный таймер 8253 для хронометража. В документе VMware отмечается, что «у программного обеспечения нет надежного способа определения его частоты. Как правило, единственный способ определить частоту локального таймера APIC — это измерить ее с помощью таймера PIT или CMOS, который дает только приблизительный результат».

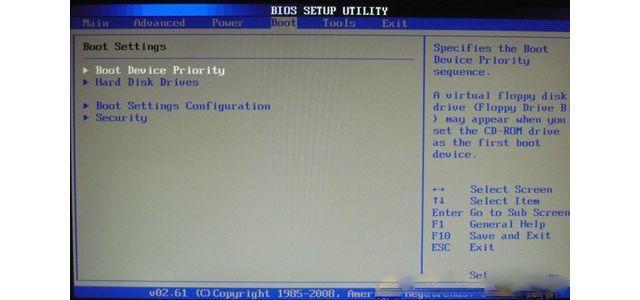

Раздел Boot

На этой вкладке изменяются настройки загрузки компьютера. В подразделе «Boot Device Priority» выставляется последовательность загрузки накопителей. Иногда последовательность приходится менять во время установки Windows, когда не получается выбрать загрузочный диск через специальное окно при старте ПК. В остальных случаях параметры можно не трогать, либо выставить приоритет для диска, на котором располагается операционная система.

«Hard Disk Drivers» – в подразделе выбирается диск, с которого следует в первую очередь пытаться загрузить ОС. Настраивается, если в системном блоке установлено несколько накопителей.

В подразделе «Boot Setting Configuration» присутствуют следующие настройки:

- Quick Boot – это опция в БИОСЕ, которая отключает проведение тестов оборудования во время запуска компьютера. Если параметр активирован, то система будет загружаться быстрее, однако пользователь не сможет увидеть описание ошибок, в случае их возникновения.

- Full Screen Logo – вместо информации об оборудовании, при запуске на экране появится логотип.

- Add On ROM Display Mode – параметр определяет последовательность отображения данных о подключенных через платы устройствах, имеющих свой BIOS.

- Bootup Num-Lock – если включено, то после запуска ПК клавиша Num-Lock будет в активном положении.

- Wait For «F1» If Error – при выявлении ошибки во время стартового тестирования, от пользователя потребуется нажатие клавиши F1 для дальнейшего запуска ОС.

- Hit «DEL» Message Display – если отключено, то при запуске на экране не будет отображаться сообщение о том, какую кнопку следует нажать для входа в БИОС.

Иногда в описанном выше подразделе можно встретить опцию «Fast Boot». Это параметр в BIOS, который аналогичен «Quick Boot», позволяющему ускорить загрузку ОС.

Настройки «Security Setting»:

- Supervisor Password – делает возможным задать пароль для входа в БИОС, ввод которого позволит изменять любые параметры.

- User Password – аналогично, только после ввода пароля будет дана возможность просмотра установленных настроек, но не их изменение.

Дискретный APIC

Чип Intel APIC первого поколения, 82489DX, который предназначался для использования с процессорами Intel 80486 и ранними процессорами Pentium, на самом деле является внешним локальным APIC и APIC ввода-вывода в одной схеме. Спецификация Intel MP 1.4 называет его «дискретным APIC» в отличие от «интегрированного APIC», присутствующего в большинстве процессоров Pentium. 82489DX имел 16 линий прерывания; у него также была особенность, заключающаяся в том, что он мог терять некоторые прерывания ISA.

В многопроцессорной системе 486 каждый процессор должен был быть сопряжен со своим собственным 82489DX; кроме того, дополнительный 82489DX должен был использоваться в качестве APIC ввода / вывода. 82489DX не мог эмулировать 8259A (XT-PIC), поэтому их также пришлось включить в качестве физических микросхем для обратной совместимости. 82489DX был упакован как 132-контактный PQFP .

Как это работает?

Рассмотрим абстрактный пример. Пусть для выполнения заданного действия необходимо записать в регистр по адресу X данные Y. При использовании подхода, основанного на вызове сервисных процедур BIOS, в выполняемом блоке BIOS будет размещена процедура, которая осуществляет указанную запись. Задача операционной системы — просто вызвать эту процедуру. В данном случае, особенности реализации конкретного чипсета, если таковые имеются, скрыты внутри BIOS и не являются заботой разработчика ОС.

Второй вариант — ОС не обращается к BIOS и выполняет указанную запись самостоятельно. В этом случае, драйвер напрямую взаимодействует с регистрами чипсета, распознает и эффективно использует его возможности. Но расплата за это — усложнение и ограниченная совместимость. Как известно, под каждый чипсет нужен свой драйвер.

Разработчикам ACPI удалось придумать третий вариант. Численные значения X и Y, отражающие особенности реализации конкретной платформы, хранятся в специальных таблицах, которые генерирует BIOS при старте и размещает в оперативной памяти. Для этого, как правило, используется последний мегабайт верхней памяти. Операционная система находит и считывает эти параметры. Процедура записи в регистр по адресу X данных Y является частью ОС, а не BIOS, но параметры X и Y предоставляет BIOS посредством таблиц ACPI.

Какие преимущества это дает? Таблицы ACPI, в отличие от сервисных процедур BIOS, не содержат выполняемого кода, поэтому независимо от архитектуры процессора и режима его работы, можно использовать одни и те же таблицы. Чтобы оценить это преимущество, вспомним о неудобствах, связанных с тем, что большинство функций BIOS могут быть вызваны только в реальном режиме процессора (Real Mode). Функции, доступные в защищенном режиме (Protected Mode) должны иметь несколько точек входа (для Real Mode, Protected Mode 16, Protected Mode 32).

Так как процедура взаимодействия с оборудованием является частью ОС, для настройки на конкретную платформу, можно совместно использовать данные, полученные от BIOS (из таблиц ACPI) и данные, размещенные в драйвере при его разработке. Это дает дополнительную гибкость.

Таким образом, таблицы ACPI обеспечивают эффективное использование BIOS для информирования программного обеспечения об особенностях конкретной платформы. При этом отсутствуют неудобства, связанные с использованием сервисных процедур BIOS.

APIC Timer Modes

The timer has 2 or 3 modes. The first 2 modes (periodic and one-shot) are supported by all local APICs. The third mode (TSC-Deadline mode) is an extension that is only supported on recent CPUs.

Periodic Mode

For periodic mode, software sets a «initial count» and the local APIC uses it for a «current count». The local APIC decrements the current count until it reaches zero, then generates a timer IRQ and resets the current count to the initial count and begins decrementing the current count again. In this way the local APIC generates IRQs at a fixed rate depending on the initial count. The current count is decremented at a rate that depends on the CPU’s external frequency («bus frequency») divided by the value in the local APIC’s «Divide Configuration Register».

For example, for a 2.4 GHz CPU with an external/bus frequency of 800 MHz, if the Divide Configuration Register is set to «divide by 4» and the initial count is set to 123456; then the local APIC timer would decrement the count at a rate of 200 MHz and generate a timer IRQ every 617.28 us, giving a rate of IRQs of 1620.01 Hz.

One-Shot Mode

For one-shot mode, the local APIC decrements the current count (and generates a timer IRQ when the count reaches zero) in the same way as in periodic mode; however it doesn’t reset the current count to the initial count when the current count reaches zero. Instead, software has to set a new count each time if it wants more timer IRQs.

The advantage of this mode is that software can have precise control over when timer IRQs occur. For example, during task switches an OS could set the count to a value that depends on the new task’s priority (so that some tasks run for a small amount of time and other tasks run for a larger amount of time), and there wouldn’t be any unwanted IRQs. Some OSs use this approach to implement a generic high precision timer service, where the local APIC count is set to a value that depends on which event will happen soonest. For example, if the currently running task switch should be pre-empted in 1234 nanoseconds, a sleeping task needs to wake up in 333 nanoseconds and alarm signal has to be sent in 44444 nanoseconds, then the timer’s count would be set to 333 nanoseconds (the earliest delay needed) and when the the timer IRQ occurs the OS knows that there’s 901 nanoseconds remaining before the current task should be pre-empted and 441111 nanoseconds until the alarm signal needs to be sent (and would set the count to 901 nanoseconds for the next timer IRQ).

The disadvantages are that it’s harder to track real-time with one-shot mode and special care needs to be taken to avoid race conditions; especially if a new count is set before the old count expires.

TSC-Deadline mode

TSC-Deadline mode is very different to the other 2 modes. Instead of using the CPU’s external/bus frequency to decrement a count, software sets a «deadline» and the local APIC generates a timer IRQ when the value of the CPU’s time stamp counter is greater than or equal to the deadline.

Despite these differences, software would/could use it in the same way that one-shot mode would be used. The advantages (compared to one-shot mode) are that you get higher precision (because the CPU’s time stamp counter runs at the CPU’s (nominal) internal frequency rather than the CPU’s external/bus frequency), and it’s easier to avoid/handle race conditions.

Local APIC configuration

The local APIC is enabled at boot-time and can be disabled by clearing bit 11 of the IA32_APIC_BASE Model Specific Register (MSR) (see example below, this only works on CPUs with family >5, as the Pentium does not have such MSR). The CPU then receives its interrupts directly from a 8259-compatible PIC. The Intel Software Developer’s Manual, however states that, once you have disabled the local APIC through IA32_APIC_BASE you can’t enable it anymore until a complete reset. The I/O APIC can also be configured to run in legacy mode so that it emulates an 8259 device.

The local APIC’s registers are memory-mapped in physical page FEE00xxx (as seen in table 8-1 of Intel P4 SPG). This address is the same for each local APIC that exists in a configuration, meaning you are only able to directly access the registers of the local APIC of the core that your code is currently executing on. Note that there is a MSR that specifies the actual APIC base (only available on CPUs with family >5). The MADT contains the local APIC base and on 64-bit systems it may also contain a field specifying a 64-bit base address override which you ought to use instead. You can choose to leave the Local APIC base just where you find it, or to move it at your pleasure. Note: I don’t think you can move it any further than the 4th Gb.

To enable the Local APIC to receive interrupts it is necessary to configure the «Spurious Interrupt Vector Register». The correct value for this field is the IRQ number that you want to map the spurious interrupts to within the lowest 8 bits, and the 8th bit set to 1 to actually enable the APIC (see the specification for more details). You should choose an interrupt number that has its lowest 4 bits set and is above 32 (as you might guess); easiest is to use 0xFF. This is important on some older processors because the lowest 4 bits for this value must be set to 1 on these.

Disable the 8259 PIC properly. This is nearly as important as setting up the APIC. You do this in two steps: masking all interrupts and remapping the IRQs. Masking all interrupts disables them in the PIC. Remapping is what you probably already did when you used the PIC: you want interrupt requests to start at 32 instead of 0 to avoid conflicts with the exceptions. You should then avoid using these interrupt vectors for other purposes. This is necessary because even though you masked all interrupts on the PIC, it could still give out spurious interrupts which will then be misinterpreted from your kernel as exceptions.

Here are some code examples on setting up the APIC:

#define IA32_APIC_BASE_MSR 0x1B

#define IA32_APIC_BASE_MSR_BSP 0x100 // Processor is a BSP

#define IA32_APIC_BASE_MSR_ENABLE 0x800

/** returns a 'true' value if the CPU supports APIC

* and if the local APIC hasn't been disabled in MSRs

* note that this requires CPUID to be supported.

*/

bool check_apic() {

uint32_t eax, edx;

cpuid(1, &eax, &edx);

return edx & CPUID_FEAT_EDX_APIC;

}

/* Set the physical address for local APIC registers */

void cpu_set_apic_base(uintptr_t apic) {

uint32_t edx = ;

uint32_t eax = (apic & 0xfffff0000) | IA32_APIC_BASE_MSR_ENABLE;

#ifdef __PHYSICAL_MEMORY_EXTENSION__

edx = (apic >> 32) & 0x0f;

#endif

cpuSetMSR(IA32_APIC_BASE_MSR, eax, edx);

}

/**

* Get the physical address of the APIC registers page

* make sure you map it to virtual memory ;)

*/

uintptr_t cpu_get_apic_base() {

uint32_t eax, edx;

cpuGetMSR(IA32_APIC_BASE_MSR, &eax, &edx);

#ifdef __PHYSICAL_MEMORY_EXTENSION__

return (eax & 0xfffff000) | ((edx & 0x0f) << 32);

#else

return (eax & 0xfffff000);

#endif

}

void enable_apic() {

/* Hardware enable the Local APIC if it wasn't enabled */

cpu_set_apic_base(cpu_get_apic_base());

/* Set the Spurious Interrupt Vector Register bit 8 to start receiving interrupts */

write_reg(0xF0, ReadRegister(0xF0) | 0x100);

}

Как настроить биос — основные разделы

MAIN — раздел для:

- непосредственной корректировки временных данных;

- определения и изменения некоторых параметров винчестеров (жестких дисков) после их выбора с помощью «стрелок» клавиатуры и нажатия кнопки «Ввод» (Enter). Рисунок 1.

В меню Main BIOS Setup вы попадаете сразу, как зайдете в БИОС

Если вы хотите перестроить режимы винчестера, то после нажатия кнопки «Ввод» вы попадете в его меню по умолчанию. Для нормальной работы необходимо выставить «стрелками» и кнопкой «Ввод» в пунктах:

- LBA Large Mode — Auto;

- Block (Multi-Sector Transfer) — Auto;

- PIO Mode — Auto;

- DMA Mode — Auto;

- 32 Bit Transfer — Enabled;

- Hard Disk Write Protect — Disabled;

- Storage Configuration — желательно не изменять;

- SATA Detect Time out — изменять нежелательно.

- Configure SATA as — выставить на AHCI.

- System Information — данные о системе, которые можно почитать.

ADVANCED — раздел непосредственных настроек основных узлов компьютера. Рисунок 2. Он состоит из подразделов:

- JumperFree Configuration — из него (нажатием кнопки «Ввод» (Enter)) попадаем в меню Configure System Frequency/Voltage, которое позволяет настраивать модули памяти и процессор. Оно состоит из пунктов:

- AI Overclocking (режимы Auto и Manual) служит для разгона процессора вручную или автоматически;

- DRAM Frequency — изменяет частоту (тактовую) шины модулей памяти;

- Memory Voltage — ручная смена напряжения на модулях памяти;

- NB Voltage — ручная смена напряжения на чипсете.

- CPU Configuration — при нажатии кнопки «Ввод» (Enter) открывается меню, в котором можно просматривать и изменять некоторые данные процессора.

- Chipset — менять не рекомендуется.

- Onboard Devices Configuration — смена настроек некоторых портов и контролеров:

- Serial Portl Address — смена адреса COM-порта;

- Parallel Port Address — смена адреса LPT-порта;

- Parallel Port Mode — смена режимов параллельного (LPT) порта и адресов некоторых других портов.

- USB Configuration — смена работы (например, включение/отключение) USB-интерфейса.

- PCIPnP — менять не рекомендуется.

Раздел Advanced зачастую содержит детальные настройки процессора, чипсета, устройств, опции по разгону и т.д.

POWER — смена настроек питания. Для нормальной работы необходимо выставить «стрелками» и кнопкой «Ввод» в пунктах:

- Suspend Mode — Auto.

- ACPI 2.0 Support — Disabled.

- ACPI APIC Support — Enabled.

- APM Configuration — изменять нежелательно.

- Hardware Monitor — корректировка общего питания, оборотов кулеров и температуры.

Programming with the 8259 PIC

Each chip (master and slave) has a command port and a data port (given in the table below). When no command is issued, the data port allows us to access the interrupt mask of the 8259 PIC.

| Chip — Purpose | I/O port |

|---|---|

| Master PIC — Command | 0x0020 |

| Master PIC — Data | 0x0021 |

| Slave PIC — Command | 0x00A0 |

| Slave PIC — Data | 0x00A1 |

- Each PIC vector offset must be divisible by 8, as the 8259A uses the lower 3 bits for the interrupt number of a particular interrupt (0..7).

- The only way to change the vector offsets used by the 8259 PIC is to re-initialize it, which explains why the code is «so long» and plenty of things that have apparently no reasons to be here.

- If you plan to return to real mode from protected mode (for any purpose), you really must restore the PIC to its former configuration.

Real Mode

| Chip | Interrupt numbers (IRQ) | Vector offset | Interrupt Numbers |

|---|---|---|---|

| Master PIC | 0 to 7 | 0x08 | 0x08 to 0x0F |

| Slave PIC | 8 to 15 | 0x70 | 0x70 to 0x77 |

These default BIOS values suit real mode programming quite well; they do not conflict with any CPU exceptions like they do in protected mode.

Protected Mode

In protected mode, the IRQs 0 to 7 conflict with the CPU exception which are reserved by Intel up until 0x1F. (It was an IBM design mistake.) Consequently it is difficult to tell the difference between an IRQ or an software error. It is thus recommended to change the PIC’s offsets (also known as remapping the PIC) so that IRQs use non-reserved vectors. A common choice is to move them to the beginning of the available range (IRQs 0..0xF -> INT 0x20..0x2F). For that, we need to set the master PIC’s offset to 0x20 and the slave’s to 0x28. For code examples, see below.

Что такое EIST?

Данная аббревиатура расшифровывается как Enhanced Intel SpeedStep Technology, что переводится на русский означает Усовершенствованная технология SpeedStep от Intel. В свою очередь SpeedStep это название технологии энергосбережения для процессора, о которой у нас уже была отдельная статья.

Так вот CPU EIST Function это продолжение SpeedStep. Основное отличие между ними это наличие в первой нескольких вариантов промежуточных напряжений и частот процессора, благодаря которым баланс между производительностью и энергосбережением будет соблюдаться более точно и менее заметно для пользователя.

То есть при слабых нагрузках производительность не будет опускаться до минимума из-за чего может наблюдаться притормаживание работы компьютера. Она снизиться лишь на несколько ступеней, благодаря чему вы не заметите этого, а в случае возрастания нагрузки выход на максимальные рабочие частоты произойдет быстрее и менее заметно.